File:Lawn-Tennis-Vertical-Sync.png

Original file (1,642 × 1,188 pixels, file size: 996 KB, MIME type: image/png)

Summary

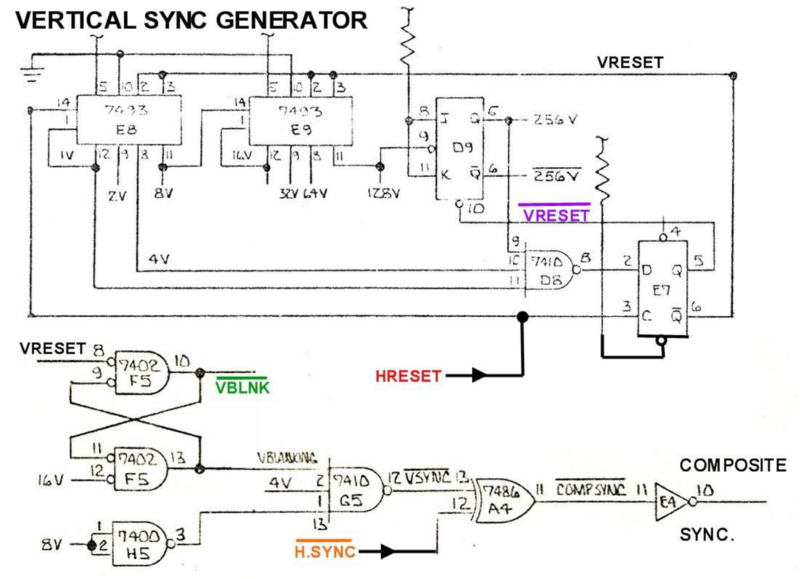

The vertical sync circuit is the same configuration as the horizontal sync system, except the drive pulse is the HRESET pulse, not the master clock or CLK.

During counting after 256 counts this sets pin 5 (the 256V connection) of D9 high, then after another 1 + 4 = 261 counts to satisfy the inputs of the 7410 NAND gate D8, the output of D8 falls low. Then on the 262nd HRESET pulse the counters are reset.

The division of the horizontal rate is therefore is 262. HRESET has a frequency of 15,731 Hz, so VRESET has a frequency of 15731/262 = 60.04 Hz which is the Field frequency for the monitor or very close to it. The horizontal and vertical sync pulses are mixed together by the XOR gate A4 to become (not)composite sync.

File history

Click on a date/time to view the file as it appeared at that time.

| Date/Time | Thumbnail | Dimensions | User | Comment | |

|---|---|---|---|---|---|

| current | 00:36, 2 January 2024 |  | 1,642 × 1,188 (996 KB) | Wikiadmin (talk | contribs) | The vertical sync circuit is the same configuration as the horizontal sync system, except the drive pulse is the HRESET pulse, not the master clock or CLK. During counting after 256 counts this sets pin 5 (the 256V connection) of D9 high, then after another 1 + 4 = 261 counts to satisfy the inputs of the 7410 NAND gate D8, the output of D8 falls low. Then on the 262nd HRESET pulse the counters are reset. The division of the horizontal rate is therefore is 262. HRESET has a frequency of 15,7... |

You cannot overwrite this file.